江波龍旗下元信電子首次亮相臺北電腦展,以創新實力迎接高容量SSD新時代

在近日舉行的2024年臺北國際電腦展(COMPUTEX TAIPEI)上,江波龍電子旗下的元信電子首次以獨立品牌形象驚艷亮相,成為展會的一大亮點。此次參展,元信電子不僅展示了其在計算機軟硬件,特別是存儲領域的深厚研發實力,更重磅發布了一系列面向未來的高容量、高性能固態硬盤(SSD)產品,正式宣告其全力進軍并引領即將到來的高容量SSD時代。

作為全球最具影響力的科技產業盛會之一,臺北電腦展一直是前沿技術與創新產品的風向標。元信電子的首秀選擇在此舞臺,彰顯了其母公司江波龍在存儲行業的戰略雄心與市場信心。展臺上,元信電子重點展示了其基于最新主控芯片和3D NAND閃存技術的高端SSD解決方案,涵蓋了從消費級到企業級的全產品線。其中,數款容量突破8TB甚至邁向更高規格的PCIe 4.0/5.0 SSD原型產品尤為引人注目,它們憑借卓越的順序讀寫速度、超低的延遲和強大的耐用性,精準回應了數據中心、人工智能計算、高清內容創作及高端游戲等場景對海量數據高速存取的迫切需求。

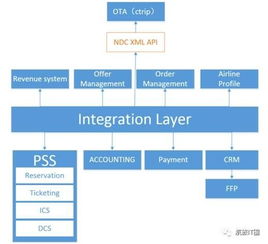

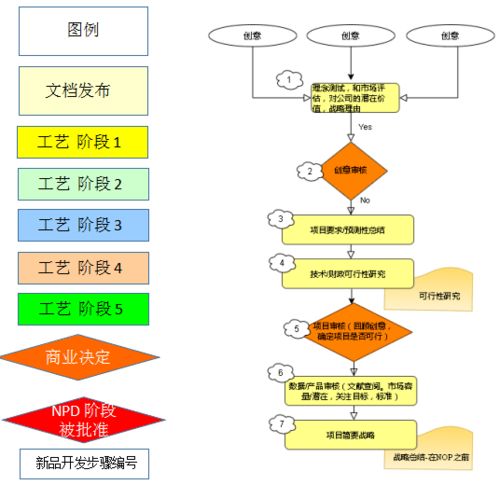

元信電子的核心競爭力,根植于江波龍集團在存儲領域長達二十余年的深厚積累。公司不僅專注于硬件研發與制造,更在固件開發、系統集成與測試驗證等軟件層面構筑了完整的技術壁壘。這種“軟硬件協同研發與銷售”的一體化模式,確保了產品從設計到交付的全鏈條優化,能夠為客戶提供高度定制化、穩定可靠的存儲解決方案。面對即將爆發的數據洪流,元信電子前瞻性地布局了QLC(四層單元)等更高密度的存儲技術,旨在以更具成本效益的方式,推動TB級容量SSD的普及,加速替代傳統機械硬盤(HDD)在溫冷數據存儲領域的地位。

此次臺北電腦展的亮相,是元信電子獨立品牌征程的重要里程碑。它向全球市場清晰地傳遞了一個信號:在存儲技術快速迭代、數據容量需求呈指數級增長的今天,元信電子已經做好了充分準備。通過持續的技術創新和對市場趨勢的敏銳把握,元信電子致力于與產業鏈伙伴攜手,共同推動存儲技術的邊界,讓更高性能、更大容量的SSD賦能千行百業的數字化轉型,真正迎接并定義屬于高容量SSD的全新時代。

如若轉載,請注明出處:http://www.zjshunyuan.cn/product/50.html

更新時間:2026-04-14 06:57:55